Contents

【問題】

【難易度】★★☆☆☆(やや易しい)

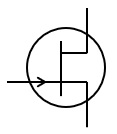

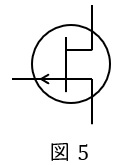

\( \ \mathrm {FET} \ \)は,半導体の中を移動する多数キャリアを\( \ \fbox { (ア) } \ \)電圧により生じる電界によって制御する素子であり,接合形と\( \ \fbox { (イ) } \ \)形がある。次の図記号は接合形の\( \ \fbox { (ウ) } \ \)チャネル\( \ \mathrm {FET} \ \)を示す。

上記の記述中の空白箇所(ア)~(ウ)に当てはまる組合せとして,正しいものを次の(1)~(5)のうちから一つ選べ。

\[

\begin{array}{cccc}

& (ア) & (イ) & (ウ) \\

\hline

(1) & ゲート & \mathrm {MOS} & \mathrm {n} \\

\hline

(2) & ドレイン & \mathrm {MSI} & \mathrm {p} \\

\hline

(3) & ソース & \mathrm {DIP} & \mathrm {n} \\

\hline

(4) & ドレイン & \mathrm {MOS} & \mathrm {p} \\

\hline

(5) & ゲート & \mathrm {DIP} & \mathrm {n} \\

\hline

\end{array}

\]

【ワンポイント解説】

\( \ \mathrm {FET} \ \)の特性や特徴を問う問題です。

本問においては細かい動作原理は問われていませんが,電験においてはそれぞれの\( \ \mathrm {FET} \ \)の動作原理は理解しておく必要があります。以下に紹介する内容は試験本番までに理解しておいて下さい。

本問は平成11問3からの再出題となります。

1.接合形\( \ \mathrm {FET} \ \)の動作原理

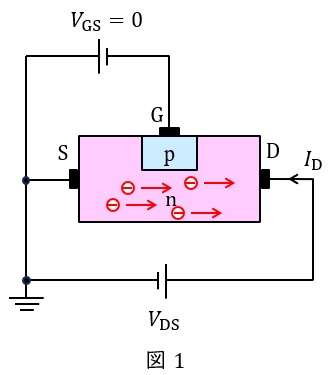

接合形\( \ \mathrm {FET} \ \)(\( \ \mathrm {n} \ \)チャネル)は,図1のように\( \ \mathrm {n} \ \)形半導体と\( \ \mathrm {p} \ \)形半導体を接合し,\( \ \mathrm {n} \ \)形半導体にソース\( \ \mathrm {S} \ \)とドレーン\( \ \mathrm {D} \),\( \ \mathrm {p} \ \)形半導体にゲート\( \ \mathrm {G} \ \)を取り付けた素子です。

図1に示すように,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)が零でドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)を加えると,\( \ \mathrm {n} \ \)形半導体内のキャリヤ(電子)が移動することでドレーン電流\( \ I_{\mathrm {D}} \ \)が流れます。

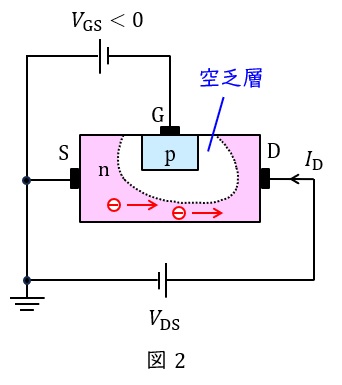

しかしながら,図2に示すようにゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)に逆電圧を加えると,\( \ \mathrm {pn} \ \)接合部に空乏層が形成されるので,ドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)を加えても\( \ \mathrm {n} \ \)形半導体の流路が狭くなり,ドレーン電流\( \ I_{\mathrm {D}} \ \)が流れにくくなります。

このように,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)の大きさを変化させることによりドレーン電流\( \ I_{\mathrm {D}} \ \)が制御できる素子となります。

2.\( \ \mathrm {MOSFET} \ \)の動作原理

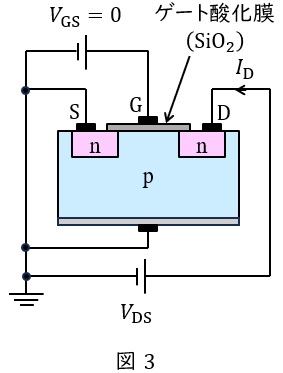

\( \ \mathrm {MOSFET} \ \)(\( \ \mathrm {n} \ \)チャネル)は,図3のように\( \ \mathrm {p} \ \)形基板表面に\( \ \mathrm {n} \ \)形のソース\( \ \mathrm {S} \ \)とドレーン\( \ \mathrm {D} \ \)を形成し,ゲート\( \ \mathrm {G} \ \)を電子や正孔を通さない薄いゲート酸化膜を介して形成する素子です。

図3のように,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)が零のとき,ドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)を加えても,\( \ \mathrm {p} \ \)形基板によりドレーン-ソース間は導通せず,ドレーン電流\( \ I_{\mathrm {D}} \ \)は流れません。

図4のように,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)を加えると,ゲート電極に電子が引き寄せられ,疑似的な\( \ \mathrm {n} \ \)形の層ができ,ドレーン-ソース間が導通するようになり,ドレーン電流\( \ I_{\mathrm {D}} \ \)が流れるようになります。そのままドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)を大きくしていっても,ある値を上限に\( \ \mathrm {n} \ \)層の導通路の幅が支配的となり,ドレーン電流\( \ I_{\mathrm {D}} \ \)は大きくなりません。

一方,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)を大きくすると,\( \ \mathrm {n} \ \)層の導通路が大きくなるので,ドレーン電流\( \ I_{\mathrm {D}} \ \)が大きくなります。

したがって,ドレーン電流\( \ I_{\mathrm {D}} \ \)はゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)でコントロールできることがわかります。

【解答】

解答:(1)

(ア)

ワンポイント解説「1.接合形\( \ \mathrm {FET} \ \)の動作原理」及び「2.\( \ \mathrm {MOSFET} \ \)の動作原理」の通り,\( \ \mathrm {FET} \ \)は,半導体の中を移動する多数キャリアをゲート電圧により制御する素子です。

(イ)

ワンポイント解説「1.接合形\( \ \mathrm {FET} \ \)の動作原理」及び「2.\( \ \mathrm {MOSFET} \ \)の動作原理」の通り,\( \ \mathrm {FET} \ \)には接合形と\( \ \mathrm {MOS} \ \)形があります。

(ウ)

問題の図記号は\( \ \mathrm {n} \ \)チャネル\( \ \mathrm {FET} \ \)の図記号です。\( \ \mathrm {p} \ \)チャネル\( \ \mathrm {FET} \ \)の図記号は図5にような図記号となります。

愛知県出身 愛称たけちゃん

詳しくは

愛知県出身 愛称たけちゃん

詳しくは