Contents

【問題】

【難易度】★★★★★(難しい)

\( \ \mathrm {NAND} \ \mathrm {IC} \ \)を用いたパルス回路について,次の(a)及び(b)の問に答えよ。ただし,高電位を「\( \ 1 \ \)」,低電位を「\( \ 0 \ \)」と表すことにする。

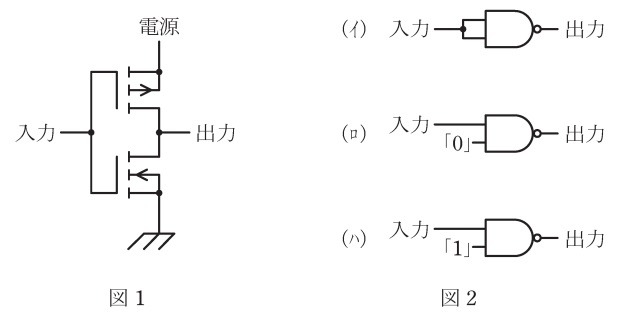

(a) \( \ \mathrm {p} \ \)チャネル及び\( \ \mathrm {n} \ \)チャネル\( \ \mathrm {MOSFET} \ \)を用いて構成された図1の回路と真理値表が同一となるものを,図2の\( \ \mathrm {NAND} \ \)回路の接続(イ),(ロ),(ハ)から選び,全て列挙したものを次の(1)~(5)のうちから一つ選べ。

(1) \((イ)\) (2) \((ロ)\) (3) \((ハ)\) (4) \((イ),(ロ)\) (5) \((イ),(ハ)\)

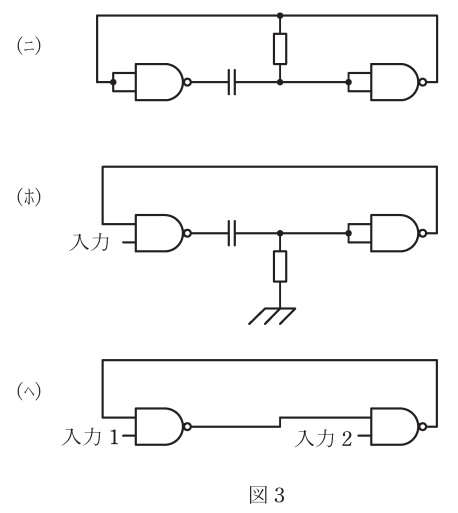

(b) 図3の三つの回路はいずれもマルチバイブレータの一種であり,これらの回路図において\( \ \mathrm {NAND} \ \mathrm {IC} \ \)の電源及び接地端子は省略している。同図(ニ),(ホ),(ヘ)の入力の数がそれぞれ\( \ 0 \ \),\( \ 1 \ \),\( \ 2 \ \)であることに注意して,これら三つの回路と次の二つの性質を正しく対応づけたものの組合せとして,正しいものを次の(1)~(5)のうちから一つ選べ。

性質Ⅰ:

出力端子からパルスが連続的に発生し,ディジタル回路の中で発振器として用いることができる。

性質Ⅱ:

「\( \ 0 \ \)」や「\( \ 1 \ \)」を記憶する機能をもち,フリップフロップの構成にも用いられる。

\[

\begin{array}{ccc}

& 性質Ⅰ & 性質Ⅱ \\

\hline

(1) & (ニ) & (ホ) \\

\hline

(2) & (ニ) & (ヘ) \\

\hline

(3) & (ホ) & (ニ) \\

\hline

(4) & (ホ) & (ヘ) \\

\hline

(5) & (ヘ) & (ホ) \\

\hline

\end{array}

\]

【ワンポイント解説】

\( \ \mathrm {NAND} \ \mathrm {IC} \ \)を用いたパルス回路に関する問題です。

理論科目というよりは,機械科目に出題されそうな内容で,\( \ \mathrm {MOSFET} \ \)の性質を知っていること,\( \ \mathrm {NAND} \ \)回路や\( \ \mathrm {NOT} \ \)回路の動作を知っていること等様々な知識が求められる総合問題と言えると思います。

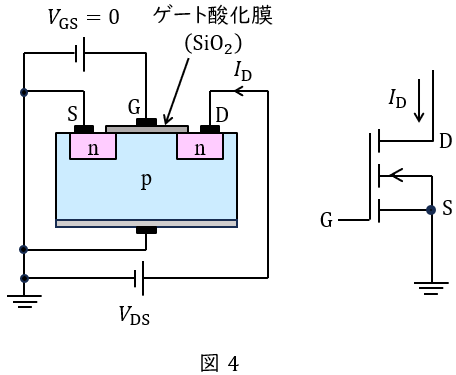

1.\( \ \mathrm {MOSFET} \ \)の動作原理

\( \ \mathrm {MOSFET} \ \)(\( \ \mathrm {n} \ \)チャネル)は,図4のように\( \ \mathrm {p} \ \)形基板表面に\( \ \mathrm {n} \ \)形のソース\( \ \mathrm {S} \ \)とドレーン\( \ \mathrm {D} \ \)を形成し,ゲート\( \ \mathrm {G} \ \)を電子や正孔を通さない薄いゲート酸化膜を介して形成する素子です。

図4のように,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)が零のとき,ドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)を加えても,\( \ \mathrm {p} \ \)形基板によりドレーン-ソース間は導通せず,ドレーン電流\( \ I_{\mathrm {D}} \ \)は流れません。

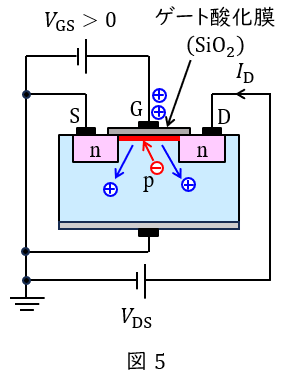

図5のように,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)を加えると,ゲート電極に電子が引き寄せられ,疑似的な\( \ \mathrm {n} \ \)形の層ができ,ドレーン-ソース間が導通するようになり,ドレーン電流\( \ I_{\mathrm {D}} \ \)が流れるようになります。そのままドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)を大きくしていっても,ある値を上限に\( \ \mathrm {n} \ \)層の導通路の幅が支配的となり,ドレーン電流\( \ I_{\mathrm {D}} \ \)は大きくなりません。

一方,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)を大きくすると,\( \ \mathrm {n} \ \)層の導通路が大きくなるので,ドレーン電流\( \ I_{\mathrm {D}} \ \)が大きくなります。

したがって,ドレーン電流\( \ I_{\mathrm {D}} \ \)はゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)でコントロールできることがわかります。

2.主な論理回路の真理値表(機械科目)

基本的な論理回路と図記号は覚える必要がありますので,以下の真理値表を覚えておきましょう。

①\( \ \mathrm {AND} \ \)回路

論理積といい,すべての入力が\( \ 1 \ \)の時のみ\( \ 1 \ \)が出力される回路で,真理値表と図記号は以下の通りです。

\[

\begin{array}{cc|c}

\mathrm {A} & \mathrm {B} & 出力 \\

\hline

0 & 0 & \color {blue }{0} \\

0 & 1 & \color {blue }{0} \\

1 & 0 & \color {blue }{0} \\

1 & 1 & \color {red}{1} \\

\end{array}

\]

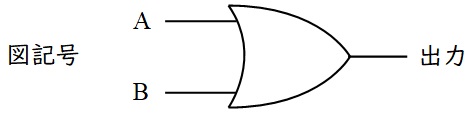

②\( \ \mathrm {OR} \ \)回路

論理和といい,入力が一つでも\( \ 1 \ \)の時\( \ 1 \ \)が出力される回路で,真理値表と図記号は以下の通りです。

\[

\begin{array}{cc|c}

\mathrm {A} & \mathrm {B} & 出力 \\

\hline

0 & 0 & \color {blue }{0} \\

0 & 1 & \color {red}{1} \\

1 & 0 & \color {red}{1} \\

1 & 1 & \color {red}{1} \\

\end{array}

\]

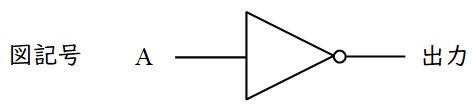

③\( \ \mathrm {NOT} \ \)回路

論理否定といい,入力を反転する回路で,真理値表と図記号は以下の通りです。

\[

\begin{array}{c|c}

\mathrm {A} & 出力 \\

\hline

0 & \color {red}{1} \\

1 & \color {blue }{0} \\

\end{array}

\]

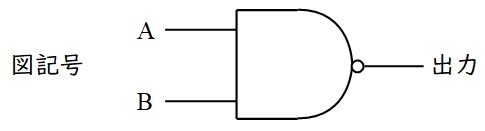

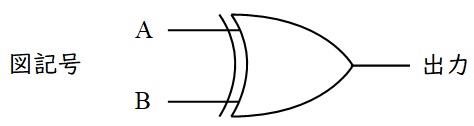

④\( \ \mathrm {NAND} \ \)回路

\( \ \mathrm {NOT}+\mathrm {AND} \ \)で\( \ \mathrm {AND} \ \)の\( \ \mathrm {NOT} \ \)を出力,すなわちすべての入力が\( \ 1 \ \)の時のみ\( \ 0 \ \)が出力される回路で,真理値表と図記号は以下の通りです。

\[

\begin{array}{cc|c}

\mathrm {A} & \mathrm {B} & 出力 \\

\hline

0 & 0 & \color {red}{1} \\

0 & 1 & \color {red}{1} \\

1 & 0 & \color {red}{1} \\

1 & 1 & \color {blue }{0} \\

\end{array}

\]

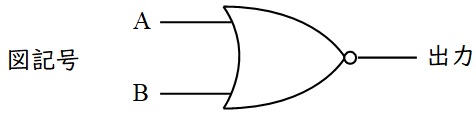

⑤\( \ \mathrm {NOR} \ \)回路

\( \ \mathrm {NOT}+\mathrm {OR} \ \)で\( \ \mathrm {OR} \ \)の\( \ \mathrm {NOT} \ \)を出力,すなわち入力が一つでも\( \ 1 \ \)の時\( \ 0 \ \)が出力される回路で,真理値表と図記号は以下の通りです。

\[

\begin{array}{cc|c}

\mathrm {A} & \mathrm {B} & 出力 \\

\hline

0 & 0 & \color {red}{1} \\

0 & 1 & \color {blue }{0} \\

1 & 0 & \color {blue }{0} \\

1 & 1 & \color {blue }{0} \\

\end{array}

\]

⑥\( \ \mathrm {ExOR} \ \)回路

排他的論理和\( \ \left( \mathrm {exclusive \ or} \right) \ \)といい,入力が異なるとき\( \ 1 \ \),入力が同じ時\( \ 0 \ \)が出力される回路で,真理値表と図記号は以下の通りです。

\[

\begin{array}{cc|c}

\mathrm {A} & \mathrm {B} & 出力 \\

\hline

0 & 0 & \color {blue }{0} \\

0 & 1 & \color {red}{1} \\

1 & 0 & \color {red}{1} \\

1 & 1 & \color {blue }{0} \\

\end{array}

\]

【解答】

(a)解答:(5)

ワンポイント解説「1.\( \ \mathrm {MOSFET} \ \)の動作」の通り,図1において,入力のゲート電圧が高電圧すなわち入力が\( \ 1 \ \)であった場合,図1の下の\( \ \mathrm {n} \ \)チャネル\( \ \mathrm {MOSFET} \ \)がオンとなり,出力は\( \ 0 \ \)となります。

一方,入力のゲート電圧が低電圧すなわち入力が\( \ 0 \ \)であった場合,図1の上の\( \ \mathrm {p} \ \)チャネル\( \ \mathrm {MOSFET} \ \)がオンとなり,出力は\( \ 1 \ \)となります。

したがって,図1は入力の反対を出力する\( \ \mathrm {NOT} \ \)回路となります。

図2において,(イ)の回路は入力が\( \ 0 \ \)の時出力が\( \ 1 \ \),入力が\( \ 1 \ \)の時出力が\( \ 0 \ \)となります。したがって\( \ \mathrm {NOT} \ \)回路となります。

(ロ)の回路は入力が\( \ 0 \ \)の時出力が\( \ 1 \ \),入力が\( \ 1 \ \)の時も出力が\( \ 1 \ \)となります。したがって\( \ \mathrm {NOT} \ \)回路となりません。

(ハ)の回路は入力が\( \ 0 \ \)の時出力が\( \ 1 \ \),入力が\( \ 1 \ \)の時出力が\( \ 0 \ \)となります。したがって\( \ \mathrm {NOT} \ \)回路となります。

よって,図2のうち図1の回路と真理値表が同一となるものは(イ)と(ハ)となります。

(b)解答:(2)

(ニ)の回路について,初期状態でコンデンサに電荷が蓄えられていないとすると,右側の\( \ \mathrm {NAND} \ \)の入力は\( \ 0 \ \)なので,右側の\( \ \mathrm {NAND} \ \)から\( \ 1 \ \)が出力されます。

そうすると,右側の\( \ \mathrm {NAND} \ \)が出力が左側の\( \ \mathrm {NAND} \ \)の入力になるため\( \ 1 \ \)が入力され,左側の\( \ \mathrm {NAND} \ \)から\( \ 0 \ \)が出力されます。

また,右側の\( \ \mathrm {NAND} \ \)の出力\( \ 1 \ \)は,抵抗を介してコンデンサに接続されているため,電荷が蓄えられることになります。

電荷が十分に蓄えられると右側の\( \ \mathrm {NAND} \ \)の入力は\( \ 1 \ \)となり,右側の\( \ \mathrm {NAND} \ \)から\( \ 0 \ \)が出力されます。

そうすると,左側の\( \ \mathrm {NAND} \ \)に\( \ 0 \ \)が入力され,左側の\( \ \mathrm {NAND} \ \)から\( \ 1 \ \)が出力され,抵抗を介してコンデンサの右端子に\( \ 0 \ \)に接続されているため,コンデンサには先程とは逆方向から電荷が蓄えられることになります。

また,十分に電荷が蓄えられると右側\( \ \mathrm {NAND} \ \)の入力が\( \ 0 \ \)となり,以後繰り返します。

これらの性質により,右側の出力\( \ 0 \ \)と\( \ 1 \ \)を繰り返すため,(ニ)の回路は発振回路となります。

(ホ)の回路について,初期状態でコンデンサに電荷が蓄えられていないとすると,右側の\( \ \mathrm {NAND} \ \)の入力は\( \ 0 \ \)なので,右側の\( \ \mathrm {NAND} \ \)から\( \ 1 \ \)が出力されます。

ここで,入力が\( \ 0 \ \)の時は,左側の\( \ \mathrm {NAND} \ \)の出力は常に\( \ 1 \ \)となり,過渡状態においてコンデンサは短絡と考えれば,右側の\( \ \mathrm {NAND} \ \)に\( \ 1 \ \)が入力され,出力は反転し\( \ 0 \ \)となります。しかしながら,左側の\( \ \mathrm {NAND} \ \)の出力は常に\( \ 1 \ \)が保持されているため,次第にコンデンサに電荷が蓄えられ,再び右側の\( \ \mathrm {NAND} \ \)の入力が\( \ 0 \ \)となり,出力は反転し\( \ 1 \ \)となります。この状態においては出力は\( \ 1 \ \)で安定することになります。

入力が\( \ 1 \ \)の時は,左側の\( \ \mathrm {NAND} \ \)の出力は\( \ 0 \ \)となり,出力が\( \ 1 \ \)で安定することになります。

(ヘ)の回路は入力\( \ 1 \ \),\( \ 2 \ \)共に\( \ 0 \ \)の時は,出力は常に\( \ 0 \ \),この状態でどちらかが\( \ 1 \ \)になっても出力は\( \ 0 \ \)を保持するため,どちらかの入力が\( \ 0 \ \)の時は常に\( \ 0 \ \)を出力することになります。

入力が共に\( \ 1 \ \)の時は,出力は\( \ 0 \ \)もしくは\( \ 1 \ \)が保持された状態となり,記憶される状態となります。

したがって,この回路は入力を適切に設定することでセットとリセットをすることができるフリップフロップとして機能することになります。

したがって,性質Ⅰを満たすのが(ニ),性質Ⅱを満たすのが(ヘ)となります。

愛知県出身 愛称たけちゃん

詳しくは

愛知県出身 愛称たけちゃん

詳しくは