Contents

【問題】

【難易度】★★☆☆☆(やや易しい)

次の文章は,電界効果トランジスタ\( \ \left( \mathrm {FET}\right) \ \)に関する記述である。

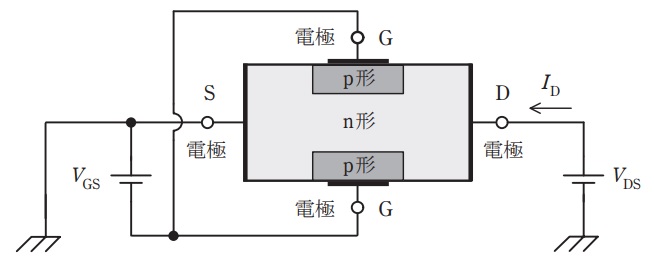

図は,\( \ \mathrm {n} \ \)チャネル接合形\( \ \mathrm {FET} \ \)の断面を示した模式図である。ドレーン\( \ \left( \mathrm {D}\right) \ \)電極に電圧\( \ V_{\mathrm {DS}} \ \)を加え,ソース\( \ \left( \mathrm {S}\right) \ \)電極を接地すると,\( \ \mathrm {n} \ \)チャネルの\( \ \fbox { (ア) } \ \)キャリヤが移動してドレーン電流\( \ I_{\mathrm {D}} \ \)が流れる。ゲート\( \ \left( \mathrm {G}\right) \ \)電極に逆方向電圧\( \ V_{\mathrm {GS}} \ \)を加えると,\( \ \mathrm {pn} \ \)接合付近に空乏層が形成されて\( \ \mathrm {n} \ \)チャネルの幅が\( \ \fbox { (イ) } \ \)し,ドレーン電流\( \ I_{\mathrm {D}} \ \)が\( \ \fbox { (ウ) } \ \)する。このことから\( \ \mathrm {FET} \ \)は\( \ \fbox { (エ) } \ \)制御形の素子である。

上記の記述中の空白箇所(ア)~(エ)に当てはまる組合せとして,正しいものを次の(1)~(5)のうちから一つ選べ。

\[

\begin{array}{ccccc}

& (ア) & (イ) & (ウ) & (エ) \\

\hline

(1) & 少数 & 減少 & 増加 & 電流 \\

\hline

(2) & 少数 & 増加 & 増加 & 電流 \\

\hline

(3) & 多数 & 増加 & 減少 & 電圧 \\

\hline

(4) & 多数 & 減少 & 減少 & 電流 \\

\hline

(5) & 多数 & 減少 & 減少 & 電圧 \\

\hline

\end{array}

\]

【ワンポイント解説】

電界効果トランジスタの動作原理に関する問題です。

\( \ \mathrm {FET} \ \)には本問に出題されているような接合形と絶縁ゲート形がありますので,合わせて覚えておくようにしましょう。

バイポーラトランジスタはベース電流で制御するため電流形,電界効果トランジスタはゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)で制御するため電圧形の素子と呼ばれます。

1.接合形\( \ \mathrm {FET} \ \)の動作原理

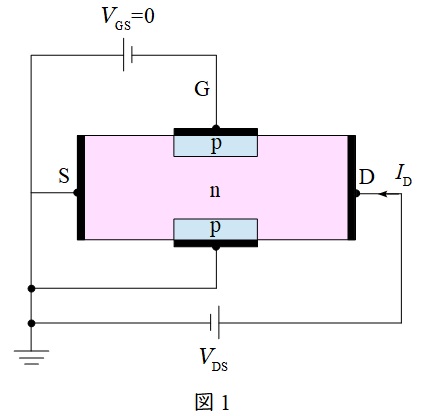

接合形\( \ \mathrm {FET} \ \)(\( \ \mathrm {n} \ \)チャネル)は図1のような構造をした\( \ \mathrm {FET} \ \)です。\( \ \mathrm {p} \ \)チャネル形は動作原理はほぼ同じで電源の向きや\( \ \mathrm {n} \ \)と\( \ \mathrm {p} \ \)が逆になる等の違いがあります。

図1のようにゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)が零である状態で,ドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)をかけると\( \ \mathrm {n} \ \)形半導体の多数キャリヤである電子の移動によりドレーン電流\( \ I_{\mathrm {D}} \ \)が流れます。

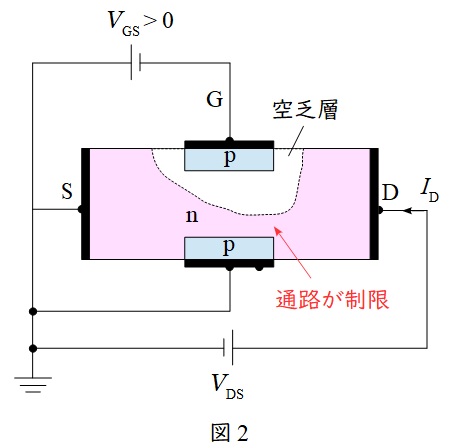

しかし,図2のようにある一定以上のゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)をかけると,負の電圧がかかっているゲート電極側の\( \ \mathrm {pn} \ \)接合部でキャリヤの再結合が発生し空乏層が形成され,\( \ \mathrm {n} \ \)形半導体の導通領域が狭くなります。これにより,ドレーン電流\( \ I_{\mathrm {D}} \ \)が流れにくくなり,ドレーン-ソース間電圧\( \ V_{\mathrm {DS}} \ \)を上げても,ドレーン電流\( \ I_{\mathrm {D}} \ \)はある一定以上は流れなくなります。

したがって,ゲート-ソース間電圧\( \ V_{\mathrm {GS}} \ \)によりドレーン電流\( \ I_{\mathrm {D}} \ \)を調整することが可能なので,電圧制御形素子と呼ばれます。

【解答】

解答:(5)

(ア)

ワンポイント解説「1.接合形\( \ \mathrm {FET} \ \)の動作原理」の通り,電圧\( \ V_{\mathrm {DS}} \ \)を加え,ソース\( \ \left( \mathrm {S}\right) \ \)電極を接地すると,\( \ \mathrm {n} \ \)形半導体の多数キャリヤである電子の移動によりドレーン電流\( \ I_{\mathrm {D}} \ \)が流れます。

(イ)

ワンポイント解説「1.接合形\( \ \mathrm {FET} \ \)の動作原理」の通り,\( \ V_{\mathrm {GS}} \ \)を加えると,\( \ \mathrm {pn} \ \)接合付近に空乏層が形成されて\( \ \mathrm {n} \ \)チャネルの幅が減少します。

(ウ)

ワンポイント解説「1.接合形\( \ \mathrm {FET} \ \)の動作原理」の通り,\( \ \mathrm {pn} \ \)接合付近に空乏層が形成されると\( \ \mathrm {n} \ \)チャネルの導通する通路が減少し,ドレーン電流\( \ I_{\mathrm {D}} \ \)は減少します。

(エ)

ワンポイント解説「1.接合形\( \ \mathrm {FET} \ \)の動作原理」の通り,\( \ \mathrm {FET} \ \)は\( \ V_{\mathrm {GS}} \ \)によりドレーン電流\( \ I_{\mathrm {D}} \ \)が調整されるので,電圧制御形の素子となります。

愛知県出身 愛称たけちゃん

詳しくは

愛知県出身 愛称たけちゃん

詳しくは